Shorter Bring-up Time at highest System Speed - PRO DESIGN’s proFPGA Cut Software simplifies and improves FPGA-based Prototyping tremendously

PRO DESIGN, leading supplier of FPGA based prototyping systems, today launched its new proFPGA Cut software, a new design partitioning front-end tool for its popular proFPGA multi-FPGA prototyping platforms. This new tool significantly reduces the design bring-up time and still offers the tremendous system speed that proFPGA users are used to.

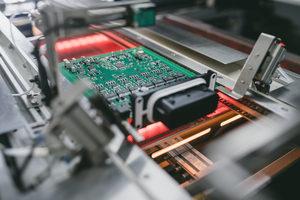

proFPGA prototyping systems handle complex ASIC and SoC designs of up to 2 Billion ASIC gates and give design and verification engineers unprecedented opportunities for high-speed verification and bug hunting to shorten the time to market by eliminating costly re-spins and providing early prototypes for software development and/or end customers.

When using FPGA-based prototyping design bring up and partitioning are the most complex, time-consuming and challenging tasks and this gets even worse because of fast-growing design sizes and required numbers of FPGAs. Typically, manual partitioning and design implementation for multi-FPGA platforms takes several days, weeks or even months without any tool support or guidance.

Many customers and users hesitate and don’t want a software tool to partition their designs because they are afraid to lose control and that the system performance suffers. The main reason why companies use FPGA-based prototyping systems in their verification and development process is the fact, that with this methodology they can reach the highest possible speed (often real-time speed), orders of magnitude faster than simulation and emulation.

There are several solutions on the market for design implementation for prototyping systems which promise an ease of use, a high automation and fast system bring-up. This is correct and these tools give users a high degree of comfort and automation. They also offer a reduction of the time to market. However, in almost all cases this negatively affects the design speed (the main reason why companies do FPGA-based prototyping).

With its new proFPGA Cut Tool, PRO DESIGN pursues a different approach. Instead of offering a completely automated “push button” flow with limited control, proFPGA Cut guides the user through the partitioning process step by step from importing RTL to exporting it for synthesis and place & route. This way the user gets 2 benefits – he still has full control over his design to allow a maximum design speed and the tool supports him to shorten this usually time consuming and complex process. proFPGA Cut offers the insertion of pin multiplexing IPs, logic optimization, constraints setting, conversion of multi-point interconnections into point-to-point interconnections, semi-automated movement of instances/ nets, etc.

With the easy-to-use proFPGA Cut GUI, all steps in the tool flow and their availability are visualized which gives the user a structured overview and workflow. A tree structure is used to display the design hierarchy and all external access ports (IOs) are shown and can be mapped into physical pins. Furthermore, the proFPGA Cut GUI displays all design interconnections between FPGAs and how they are physically mapped.

One big differentiator and advantage of the proFPGA Cut tool is that it works on RTL and not on netlist level. Therefore it is independent of the FPGA platform. That means, it can handle different FPGA technologies and a combination of these.

The new proFPGA Cut software is optimized for proFPGA hardware and takes full advantage of the system’s modular and flexible interconnection architecture and besides the GUI mode, the tool also offers a command line mode which allows the user to script all processes and to fully integrate it into their automated design flows.

"Customers have been asking us for several years about an own proFPGA partitioning tool, because manual partitioning becomes more and more complex and time-consuming. Therefore, we are now more than happy and very proud, that after a development time of about 3 years we can now release our new proFPGA Cut partitioning tool. Many of our existing and future proFPGA prototyping customers will benefit from it, it will help them to solve the increasing challenges of FPGA-based prototyping and to reduce their bring-up time." stated Gunnar Scholl, CEO of PRO DESIGN.

More Information about proFPGA CUT >>

*****

About proFPGA

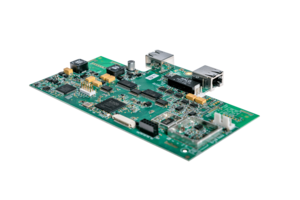

The proFPGA product family is a complete, scalable, and modular multi-FPGA prototyping solution, which fulfills the highest needs in the areas of ASIC and IP Prototyping and pre-silicon software development. The proFPGA product series consists of different types of motherboards, various Xilinx® Virtex®, Kintex® and Zynq™ UltraScale+™ / UltraScale™ / 7-series, and Intel® Stratix® and Arria® 10 FPGA modules, a large selection of daughter boards and interconnection boards/cables. It addresses customers who need a scalable and flexible high-performance FPGA-based prototyping solution for early software development and for IP/ASIC verification. The innovative system concept and technology offers best-in-class reusability across projects, guaranteeing the best return on investment.

For more information, please visit: https://www.proFPGA.com

About PRO DESIGN

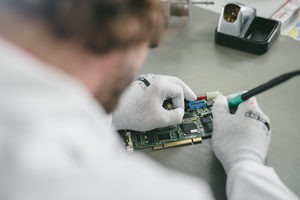

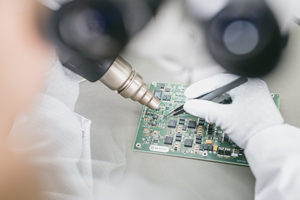

The privately-held company was founded in 1982 and has about 100 employees at various facilities in Germany, France, and the US. PRO DESIGN has more than 37 years of experience in the EDA market, and as a provider in the E²MS market. The company has built-up extensive knowledge in the areas of FPGA board development, electronic engineering, FPGA design, high-speed PCB design, mechanical construction/design, production/assembly and testing.

Contact:

Gunnar Scholl

PRO DESIGN Electronic GmbH

Tel: +4980628080

gscholl@prodesign-europe.com

Intel®, Stratix® and Arria® are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Xilinx®, Virtex®, Zynq™, Kintex®, UltraScale+™ and UltraScale™ are trademarks of Xilinx Corporation or its subsidiaries in the U.S. and/or other countries.

*Other names and brands may be claimed as the property of others.